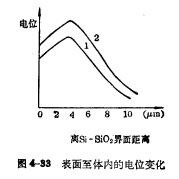

NMOS工艺,NMOS优缺点,N沟道工艺是MOS电路较早就选择工艺,因为理论上电子迁移率大得多,可以制成大跨导的MOS器件。但由于Si-SiO2界面处存在正电荷,往往容易造成N沟道耗尽型,而要制成N沟道增强型却比较困难。因此,早期的发展速度不如PMOS电路,但终因它有突出的优点,随着MOS技术的发展,目前速度较高的大规模 MOS集成电路中,NMOS已占重要的地位。

NMOS工艺,NMOS优缺点,N沟道工艺是MOS电路较早就选择工艺,因为理论上电子迁移率大得多,可以制成大跨导的MOS器件。但由于Si-SiO2界面处存在正电荷,往往容易造成N沟道耗尽型,而要制成N沟道增强型却比较困难。因此,早期的发展速度不如PMOS电路,但终因它有突出的优点,随着MOS技术的发展,目前速度较高的大规模 MOS集成电路中,NMOS已占重要的地位。

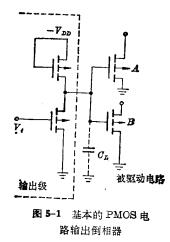

PMOS工艺,PMOS优缺点,在MOS电路的发展过程中,发展最早、最快的是PMOS集成电路,PMOS电路的生产基本上是硅平面工艺,通常称为MOS常规工艺,它具有工艺简单,设备不复杂、易于控制等优点。但PMOS电路存在着速度太低的突出缺点,对发展速度高、性能好的MOS 大规模集成电路带来很大困难。为了提高电路速度和性能,科学家们对MOS 工艺进行了一系列的革新。采用了一些新材料和工艺。

PMOS工艺,PMOS优缺点,在MOS电路的发展过程中,发展最早、最快的是PMOS集成电路,PMOS电路的生产基本上是硅平面工艺,通常称为MOS常规工艺,它具有工艺简单,设备不复杂、易于控制等优点。但PMOS电路存在着速度太低的突出缺点,对发展速度高、性能好的MOS 大规模集成电路带来很大困难。为了提高电路速度和性能,科学家们对MOS 工艺进行了一系列的革新。采用了一些新材料和工艺。

超大规模集成电路设计的基本原理简介,MOS技术发展的速度是很惊人的,MOS集成电路在性能和集成度方面,大约每年要翻一番。在七十年代,MOS芯片已经从最初速度较低(ms数量级)、集成度不高的移位寄存器、门电路和触发器,发展到了速度相当高(ns数量级)、集成度为上万个元件的微处理机芯片。七十年代末期,MOS技术已向采用5V单电源的N沟道超大规模集成电路方面发展,这种电路能以低于100ns的周期执行复杂

超大规模集成电路设计的基本原理简介,MOS技术发展的速度是很惊人的,MOS集成电路在性能和集成度方面,大约每年要翻一番。在七十年代,MOS芯片已经从最初速度较低(ms数量级)、集成度不高的移位寄存器、门电路和触发器,发展到了速度相当高(ns数量级)、集成度为上万个元件的微处理机芯片。七十年代末期,MOS技术已向采用5V单电源的N沟道超大规模集成电路方面发展,这种电路能以低于100ns的周期执行复杂

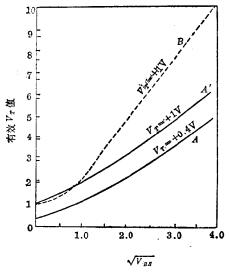

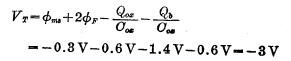

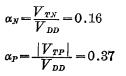

CMOS阈值电压的设计,要使设计的电路版图在性能上达到设计指标的要求,必须进行工艺设计,从而确定合理的材料参数、工艺参数和工艺条件。其中,阀值电压的控制是CMOS电路工艺设计的核心。其它材料参数和工艺参数许多是根据的要求定出来的,所以在这里主要介绍阈值电压的设计。至于材料参数和工艺参数及工艺条件,将在下一章中分别介绍。

CMOS阈值电压的设计,要使设计的电路版图在性能上达到设计指标的要求,必须进行工艺设计,从而确定合理的材料参数、工艺参数和工艺条件。其中,阀值电压的控制是CMOS电路工艺设计的核心。其它材料参数和工艺参数许多是根据的要求定出来的,所以在这里主要介绍阈值电压的设计。至于材料参数和工艺参数及工艺条件,将在下一章中分别介绍。

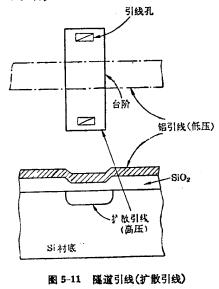

CMOS版图设计,CMOS版图设计概,CMOS是微功耗电路,对功耗的要求特别严格。造成功耗大的主要因素是静态泄漏电流。因此,在工艺和版图设计时,特别要注意采取适当措施,使漏电尽可能减到最小。图5-15所示为产生漏电的主要途径。其中image.png分别表示负载管和输入管沟道以外的氧化层下面的漏电;image.png和image.png分别表示P+源(或P+漏)与P-阱,N+源(或N+漏)与N-衬底

CMOS版图设计,CMOS版图设计概,CMOS是微功耗电路,对功耗的要求特别严格。造成功耗大的主要因素是静态泄漏电流。因此,在工艺和版图设计时,特别要注意采取适当措施,使漏电尽可能减到最小。图5-15所示为产生漏电的主要途径。其中image.png分别表示负载管和输入管沟道以外的氧化层下面的漏电;image.png和image.png分别表示P+源(或P+漏)与P-阱,N+源(或N+漏)与N-衬底

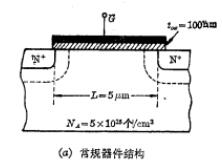

CMOS电路器件,CMOS电路计算方法,设计CMOS电路,在一般情况下,根据用户要求和给定的电路指标,首先对电路中各器件进行设计,然后画出版图,最后定出工艺参数。本节主要介绍CMOS电路器件设计和版图设计。

CMOS电路器件,CMOS电路计算方法,设计CMOS电路,在一般情况下,根据用户要求和给定的电路指标,首先对电路中各器件进行设计,然后画出版图,最后定出工艺参数。本节主要介绍CMOS电路器件设计和版图设计。

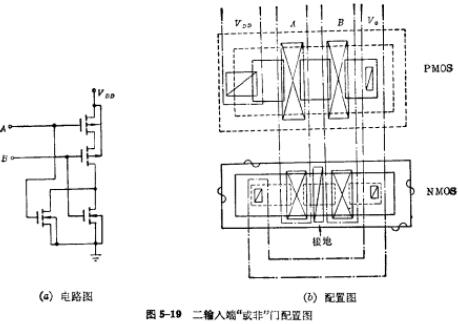

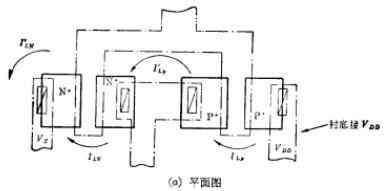

PMOS版图,PMOS版图设计PMOS版图设计装置的制作方法,版图设计是按照设计的要求和工艺条件,选择合适的尺寸,确定器件几何图形,进行合理的布局和连线,构成电路总版图,并按照工艺流程设计出一套光刻掩膜版。正确、良好的版图设计,不仅是实现电路功能所必需,而且对成品率、集成度以及电路性能都有很大的影响。

PMOS版图,PMOS版图设计PMOS版图设计装置的制作方法,版图设计是按照设计的要求和工艺条件,选择合适的尺寸,确定器件几何图形,进行合理的布局和连线,构成电路总版图,并按照工艺流程设计出一套光刻掩膜版。正确、良好的版图设计,不仅是实现电路功能所必需,而且对成品率、集成度以及电路性能都有很大的影响。

PMOS集成电路设计,PMOS集成电路的版图,MOS集成电路的设计,一般应包括逻辑设计、器件设计、版图设计和工艺设计等诸方面。若电路图已经给定,则设计的任务就归结为确定电路中各器件的尺寸(主要是沟道的宽长此)、面出器件的图形、进行排版、绘出合理的电路总版图(掩膜复合版)等。以便提供工艺所采用的光刻掩膜和考虑能够达到电路指标的工艺条件。

PMOS集成电路设计,PMOS集成电路的版图,MOS集成电路的设计,一般应包括逻辑设计、器件设计、版图设计和工艺设计等诸方面。若电路图已经给定,则设计的任务就归结为确定电路中各器件的尺寸(主要是沟道的宽长此)、面出器件的图形、进行排版、绘出合理的电路总版图(掩膜复合版)等。以便提供工艺所采用的光刻掩膜和考虑能够达到电路指标的工艺条件。

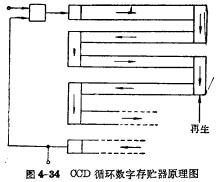

CCD应用概述,电荷耦合器件CCD,CCD的应用主要基于它的三个独特的效应—存贮效应、转移效应和光电效应,目前主要应用于信息处理、信息存贮和摄象等三个方面。

CCD应用概述,电荷耦合器件CCD,CCD的应用主要基于它的三个独特的效应—存贮效应、转移效应和光电效应,目前主要应用于信息处理、信息存贮和摄象等三个方面。

CCD MOS基本参数,CCD基本参数,CCD结构,CCD的基本参数所涉及的因素很多,有些是相互牵连的,所以在这里不可能作详细分析讨论。下面仅简要地介绍一些参数的概念。CCD的主要性能参数有阀值电压、电荷转移开元游戏官网、工作频率范围和负载量等。

CCD MOS基本参数,CCD基本参数,CCD结构,CCD的基本参数所涉及的因素很多,有些是相互牵连的,所以在这里不可能作详细分析讨论。下面仅简要地介绍一些参数的概念。CCD的主要性能参数有阀值电压、电荷转移开元游戏官网、工作频率范围和负载量等。