SOS技术制造CMOS电路工艺分析,SOS技术是“蓝宝石上外延硅”的简称。这种技术是在抛光的蓝宝石片上外延生长一层硅单晶薄层,接着将单晶薄层腐蚀成一个个彼此隔离的“小岛”,然后在“小岛”上制成各种器件,最后用金属互连构成集成电路。

SOS技术制造CMOS电路工艺分析,SOS技术是“蓝宝石上外延硅”的简称。这种技术是在抛光的蓝宝石片上外延生长一层硅单晶薄层,接着将单晶薄层腐蚀成一个个彼此隔离的“小岛”,然后在“小岛”上制成各种器件,最后用金属互连构成集成电路。

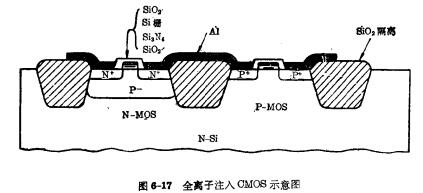

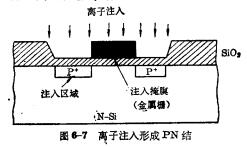

离子注入法制造CMOS电路分析,在常规工艺中,P阱区是用淡硼扩散形成的,扩散浓度的误差较大,要准确控制在1015个/cm2左右是比较困难的,造成阈值电压不易匹配。因此,有必要用离子注入法来形成P阱,以替代淡硼扩散。由于离子注入掺杂的剂量可以很精确地控制,因此大大提高了N沟道MOS管阈值电压的一致性。离子注入的剂量可以根据阈值电压image.png的要求计算出来。

离子注入法制造CMOS电路分析,在常规工艺中,P阱区是用淡硼扩散形成的,扩散浓度的误差较大,要准确控制在1015个/cm2左右是比较困难的,造成阈值电压不易匹配。因此,有必要用离子注入法来形成P阱,以替代淡硼扩散。由于离子注入掺杂的剂量可以很精确地控制,因此大大提高了N沟道MOS管阈值电压的一致性。离子注入的剂量可以根据阈值电压image.png的要求计算出来。

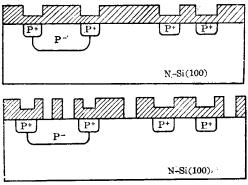

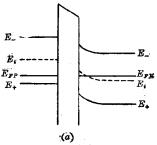

CMOS工艺,CMOS工艺流程,CMOS电路是P沟道器件和N沟道器件的组合,它具有速度高、功耗低、抗干扰能力强等突出的优点。在常规CMOS工艺中,表面电荷对阈值电压数值的影响很大。由前面讨论知道,(111)面的image.png典型值为4×1011个/cm2,而(100)面的image.png为1×1011个/cm3。

CMOS工艺,CMOS工艺流程,CMOS电路是P沟道器件和N沟道器件的组合,它具有速度高、功耗低、抗干扰能力强等突出的优点。在常规CMOS工艺中,表面电荷对阈值电压数值的影响很大。由前面讨论知道,(111)面的image.png典型值为4×1011个/cm2,而(100)面的image.png为1×1011个/cm3。

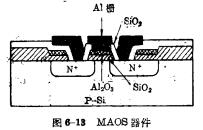

AMOS工艺,AMOS工艺流程,1.AI2O3的主要特点AMOS工艺是用SiO2-AI2O3双层结构作为MOS器件栅介质的工艺。采用这种工艺主要是基于AI2O3较SiO2有许多优越性。AMOS工艺。主要可归纳为三个主要特点:①AI2O3膜中含有负电荷,所以采用与SiO2膜具有一定厚度比例的复合结构,可以使电荷相互补偿,大大降低等效表面电荷密度,甚至可以降到零,可作为控制MOS器件阈值电压的有效方法

AMOS工艺,AMOS工艺流程,1.AI2O3的主要特点AMOS工艺是用SiO2-AI2O3双层结构作为MOS器件栅介质的工艺。采用这种工艺主要是基于AI2O3较SiO2有许多优越性。AMOS工艺。主要可归纳为三个主要特点:①AI2O3膜中含有负电荷,所以采用与SiO2膜具有一定厚度比例的复合结构,可以使电荷相互补偿,大大降低等效表面电荷密度,甚至可以降到零,可作为控制MOS器件阈值电压的有效方法

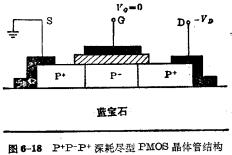

NMOS工艺,NMOS工艺器件,NMOS工艺是采用SiO2-Si3N4双层结构作为MOS器件栅介质的工艺。这种工艺主要是基于氮化硅较二氧化硅优点更多,更为现想。NMOS工艺,与常规MOS工艺相差不多,只是多了淀积Si3N4和腐蚀Si3N4两个工艺程序。下面以P沟道增强型器件为例,说明双层栅SiO2-Si3N4结构的工艺过程。淀积Si3N4是在栅氧化以后进行的。Si3N4淀积以后,接着再淀积一层Si

NMOS工艺,NMOS工艺器件,NMOS工艺是采用SiO2-Si3N4双层结构作为MOS器件栅介质的工艺。这种工艺主要是基于氮化硅较二氧化硅优点更多,更为现想。NMOS工艺,与常规MOS工艺相差不多,只是多了淀积Si3N4和腐蚀Si3N4两个工艺程序。下面以P沟道增强型器件为例,说明双层栅SiO2-Si3N4结构的工艺过程。淀积Si3N4是在栅氧化以后进行的。Si3N4淀积以后,接着再淀积一层Si

MOS源、漏区实现栅自对准,自对准mosfet,用离子注入法制造MOS器件的源、漏区,可以实现栅自对准。自对准mosfet。但完全由离子注入形成源、漏区的MOS结构是很不理想的。

MOS源、漏区实现栅自对准,自对准mosfet,用离子注入法制造MOS器件的源、漏区,可以实现栅自对准。自对准mosfet。但完全由离子注入形成源、漏区的MOS结构是很不理想的。

MOS器件的VT的应用,在MOS工艺中,离子注入技术不仅可以用来制作NMOS或PMOS的源、漏区和CMOS的P阱区,而且可以控制较低的阈值电压VT,便于与TTL电路相容。这种技术只要对常规工艺作较小的更动,就能方便地与其它MOS工艺相配合,在一块晶片上制作同一类型沟道的增强型和耗尽型器件(即E/DMOS电路)。若将离子束聚焦得很精细,采用细束扫描,进行有选择地注入,就成为无掩膜制造技术,大大简化了

MOS器件的VT的应用,在MOS工艺中,离子注入技术不仅可以用来制作NMOS或PMOS的源、漏区和CMOS的P阱区,而且可以控制较低的阈值电压VT,便于与TTL电路相容。这种技术只要对常规工艺作较小的更动,就能方便地与其它MOS工艺相配合,在一块晶片上制作同一类型沟道的增强型和耗尽型器件(即E/DMOS电路)。若将离子束聚焦得很精细,采用细束扫描,进行有选择地注入,就成为无掩膜制造技术,大大简化了

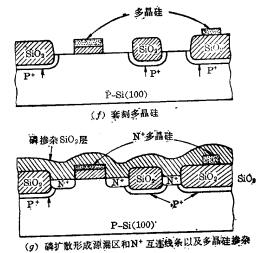

N沟道MOS,硅栅N沟MOS工艺,,N沟道等平面工艺,又称”选择氧化法MOS技术”,它的特点是在硅衬底的某一部分有选择地进行氧化,而在不需要氧化的区域用image.png掩膜保护起来。它的基本方法由图6-5表示。首先在硅衬底上淀积一层薄的image.png膜,厚度约为0.2~0.9μm,然后,刻去需要氧化部分的image.png膜,接着用热氧化法进行氧化,生成一层约为1.0μm~1.1μm的氧化层

N沟道MOS,硅栅N沟MOS工艺,,N沟道等平面工艺,又称”选择氧化法MOS技术”,它的特点是在硅衬底的某一部分有选择地进行氧化,而在不需要氧化的区域用image.png掩膜保护起来。它的基本方法由图6-5表示。首先在硅衬底上淀积一层薄的image.png膜,厚度约为0.2~0.9μm,然后,刻去需要氧化部分的image.png膜,接着用热氧化法进行氧化,生成一层约为1.0μm~1.1μm的氧化层

P沟道“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。(1)一次氧化抛光好的Si型出片(5~8Ω·cm)经清洁处理后,采用干-湿-干氧化程序,生长1μm的SiO2层。这样厚的氧化物,不仅作为扩散掩蔽,而且作为最终的场氧化物,对于减少寄生沟道是有利的。

P沟道“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。(1)一次氧化抛光好的Si型出片(5~8Ω·cm)经清洁处理后,采用干-湿-干氧化程序,生长1μm的SiO2层。这样厚的氧化物,不仅作为扩散掩蔽,而且作为最终的场氧化物,对于减少寄生沟道是有利的。

硅栅工艺,硅栅工艺的优点,“硅栅工艺”是采用掺杂的多晶硅来做MOS管栅电极的一种工艺,与上面介绍的常规铝栅工艺的不同点是先在硅片上生长一层薄的二氧化硅层(栅介质),接着淀积约为500nm的多晶硅薄层,然后刻出源、漏扩散区进行源漏扩散。“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。

硅栅工艺,硅栅工艺的优点,“硅栅工艺”是采用掺杂的多晶硅来做MOS管栅电极的一种工艺,与上面介绍的常规铝栅工艺的不同点是先在硅片上生长一层薄的二氧化硅层(栅介质),接着淀积约为500nm的多晶硅薄层,然后刻出源、漏扩散区进行源漏扩散。“硅栅工艺”对于器件和集成电路的性能,较之常规的铝栅工艺,具有较多的特点。