MOS场效应管阈值电压,对于增强型管子来说,阈值电压就是开启电压VT,对于耗尽型管而言,阈值电压就是夹断电压VT,为方便起见,也用VT表示。阈值电压VT定义为,当VDS=0时,要使源和漏之间半导体表面刚开始形成强反型的导电沟道所需加的栅极电压称为阈值电压。阈值电压是MOS器件的一个重要参数,它与器件工艺参数有密切的关系。

MOS场效应管阈值电压,对于增强型管子来说,阈值电压就是开启电压VT,对于耗尽型管而言,阈值电压就是夹断电压VT,为方便起见,也用VT表示。阈值电压VT定义为,当VDS=0时,要使源和漏之间半导体表面刚开始形成强反型的导电沟道所需加的栅极电压称为阈值电压。阈值电压是MOS器件的一个重要参数,它与器件工艺参数有密切的关系。

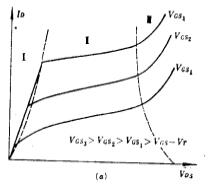

MOS场效应管的特性曲线,以n沟道增强型MOS管为例进行讨论。MOS场效应管在应用中有多种连接方式,最常用的是共源连接方式,如图1.1-7所示。图中源极与衬底相连接,信号由栅极G输入,经MOS场效应管放大后由漏极D输出。当GS电压VGS变化时,n沟增强型MOS场效应管的输出特性曲线如图1.1-8b所示。其转移特性曲线如图1.1-8b所示,它反映了漏源电流ID与栅偏压VGS的关系。图中VT称为阈值电

MOS场效应管的特性曲线,以n沟道增强型MOS管为例进行讨论。MOS场效应管在应用中有多种连接方式,最常用的是共源连接方式,如图1.1-7所示。图中源极与衬底相连接,信号由栅极G输入,经MOS场效应管放大后由漏极D输出。当GS电压VGS变化时,n沟增强型MOS场效应管的输出特性曲线如图1.1-8b所示。其转移特性曲线如图1.1-8b所示,它反映了漏源电流ID与栅偏压VGS的关系。图中VT称为阈值电

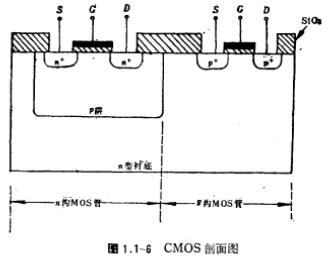

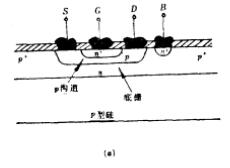

MOS场效应管的类型,这种管子以n型半导体作为衬底材料、源和漏区是p+扩散区,将图1.1-3中的n+换成p+,p型硅换成n型硅,而且n沟道换成p沟道,即得P沟道MOS场效应管结构剖面图.它也属于增强型管子,因为在栅极电压为零时,源和漏区之间不存在导电沟道。在正常工作时,源一般也接地,漏区接负电位。栅极上加负电位时,在n型半导体表面有一个指向外面的表面电场,使表面耗尽,甚至可以反型,当image.p

MOS场效应管的类型,这种管子以n型半导体作为衬底材料、源和漏区是p+扩散区,将图1.1-3中的n+换成p+,p型硅换成n型硅,而且n沟道换成p沟道,即得P沟道MOS场效应管结构剖面图.它也属于增强型管子,因为在栅极电压为零时,源和漏区之间不存在导电沟道。在正常工作时,源一般也接地,漏区接负电位。栅极上加负电位时,在n型半导体表面有一个指向外面的表面电场,使表面耗尽,甚至可以反型,当image.p

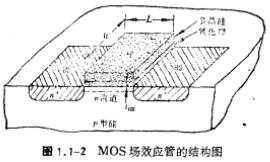

MOS场效应管的工作原理,用平面工艺制作的MOS场效应管,其典型结构图如图1.1-2所示,其中衬底材料为p型半导体,两个n+区由扩散工艺形成,分别称为源区和漏区。栅氧化层上面是金属电极,称为栅极.栅氧化层下面及源、漏之间的区开元游戏官网常称为沟道区。源及漏区分别由金属欧姆接触形成S板、D极。MOS场效应管工作原理。衬底引出的电极称为B,通常B与源是短接并且接地,但有时也将源n+与衬底B之间加上反偏电压,此

MOS场效应管的工作原理,用平面工艺制作的MOS场效应管,其典型结构图如图1.1-2所示,其中衬底材料为p型半导体,两个n+区由扩散工艺形成,分别称为源区和漏区。栅氧化层上面是金属电极,称为栅极.栅氧化层下面及源、漏之间的区开元游戏官网常称为沟道区。源及漏区分别由金属欧姆接触形成S板、D极。MOS场效应管工作原理。衬底引出的电极称为B,通常B与源是短接并且接地,但有时也将源n+与衬底B之间加上反偏电压,此

MOS场效应管的基本原理通常,品体管可分成两大类,一类称为“双极型”晶体管,这种晶体管在工作时,电子与空穴部参加导电;另一类称为“场效应”晶体管,它是利用改变垂直于导电沟道的电场来控制导电沟道的导电能力,从而实现放大的一种半导体器件。MOS场效应管的基本原理。这种晶体管在工作时只有一种载流子——电子或空穴——起着输运电流的主要作用,故“场效应“晶体管又称为“单极型”晶体管,意即只有一种极性的载流子

MOS场效应管的基本原理通常,品体管可分成两大类,一类称为“双极型”晶体管,这种晶体管在工作时,电子与空穴部参加导电;另一类称为“场效应”晶体管,它是利用改变垂直于导电沟道的电场来控制导电沟道的导电能力,从而实现放大的一种半导体器件。MOS场效应管的基本原理。这种晶体管在工作时只有一种载流子——电子或空穴——起着输运电流的主要作用,故“场效应“晶体管又称为“单极型”晶体管,意即只有一种极性的载流子

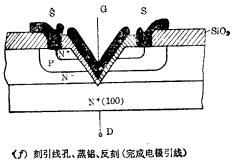

(1)一次氧化在以(100)面的N+-Si为基片的N-外延层上,生长一层二氧化硅掩膜。如图6-26(a)所示。(2)光刻、硼扩散硼扩散,形成衬底P区,扩散深度约为2μm左右。如图6-26(b)所示(3)光刻、磷扩散磷扩散,形成源区,结深约为1μm左右,并作低温淀积,生成二氧化硅保护膜。如图6-26(c)所示。(4)光刻、腐蚀V形槽光刻V形槽窗口,用水合联氨腐蚀V形槽。如图6-26(d)所示。(5)

(1)一次氧化在以(100)面的N+-Si为基片的N-外延层上,生长一层二氧化硅掩膜。如图6-26(a)所示。(2)光刻、硼扩散硼扩散,形成衬底P区,扩散深度约为2μm左右。如图6-26(b)所示(3)光刻、磷扩散磷扩散,形成源区,结深约为1μm左右,并作低温淀积,生成二氧化硅保护膜。如图6-26(c)所示。(4)光刻、腐蚀V形槽光刻V形槽窗口,用水合联氨腐蚀V形槽。如图6-26(d)所示。(5)

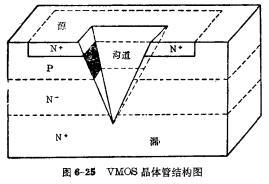

VMOS工艺结构与特点详解及分析,随着MOS大规模集成电路和超大规模集成电路的日益发展,如何进一步缩小电路中器件的尺寸和提高电路的工作速度,成为一个重要课题。一般的平面MOS工艺,在这方面都遇到了困难,比如沟道长度不能太短,因为一方面受到光刻精度的限制,另一方面又受到器件本身短沟道效应的限制。在七十年代末期,人们研制的纵向VMOS器件,完全可以克服上述困难。这是一种三维器件,沟道长度可缩短到1um

VMOS工艺结构与特点详解及分析,随着MOS大规模集成电路和超大规模集成电路的日益发展,如何进一步缩小电路中器件的尺寸和提高电路的工作速度,成为一个重要课题。一般的平面MOS工艺,在这方面都遇到了困难,比如沟道长度不能太短,因为一方面受到光刻精度的限制,另一方面又受到器件本身短沟道效应的限制。在七十年代末期,人们研制的纵向VMOS器件,完全可以克服上述困难。这是一种三维器件,沟道长度可缩短到1um

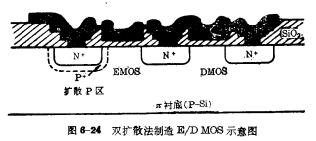

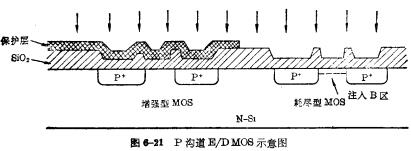

双扩散法制造E/DMOS双扩散法,简称DMOS工艺。衬底采用P-硅片(称为χ衬底),这样低浓度的P-型衬底,更容易制成N沟道耗尽型MOS器件。为了要制成增强型器件,可先在源区扩散硼,使其变成P区,然后再进行磷扩散,做成源、漏区。这样,从源到漏的杂质分布为N+-P-P--N+,增强型N沟道的阈值电压由扩散P区的杂质浓度决定,源漏之间的有效沟道长度,也由杂质扩散来调节。在源区没有进行P型杂质扩散的N沟

双扩散法制造E/DMOS双扩散法,简称DMOS工艺。衬底采用P-硅片(称为χ衬底),这样低浓度的P-型衬底,更容易制成N沟道耗尽型MOS器件。为了要制成增强型器件,可先在源区扩散硼,使其变成P区,然后再进行磷扩散,做成源、漏区。这样,从源到漏的杂质分布为N+-P-P--N+,增强型N沟道的阈值电压由扩散P区的杂质浓度决定,源漏之间的有效沟道长度,也由杂质扩散来调节。在源区没有进行P型杂质扩散的N沟

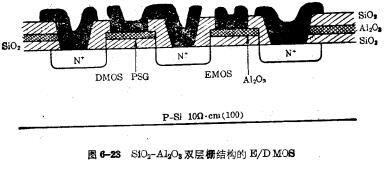

SiO2-AI2O3双层栅E/DMOS,由于AI2O3层内含有负电荷,可以抵消SiO2中的正电荷,因此可以控制SiO2和AI2O3的厚度比,从而使NMOS的阀值电压成为正值。图6-28是用SiO2-AI2O3。技术

SiO2-AI2O3双层栅E/DMOS,由于AI2O3层内含有负电荷,可以抵消SiO2中的正电荷,因此可以控制SiO2和AI2O3的厚度比,从而使NMOS的阀值电压成为正值。图6-28是用SiO2-AI2O3。技术

离子注入法制造E/DMOS电路分析,在同一块衬底上制造相同沟道的增强型与耗尽型MOS器件,即E/D型的MOS电路,这比一般MOS工艺要困难得多。因此在MOS工艺发展的初期,E/DMOS电路的发展速度比较缓慢。但随着MOS技术的日开元游戏官网异,目前已有几种制造E/DMOS电路的工艺方法。

离子注入法制造E/DMOS电路分析,在同一块衬底上制造相同沟道的增强型与耗尽型MOS器件,即E/D型的MOS电路,这比一般MOS工艺要困难得多。因此在MOS工艺发展的初期,E/DMOS电路的发展速度比较缓慢。但随着MOS技术的日开元游戏官网异,目前已有几种制造E/DMOS电路的工艺方法。