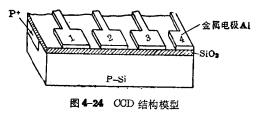

电荷耦合器件的工作原理,电荷耦合器件结构,电荷耦合器件(CCD),是1970年提出来的一种MOS结构的新型器件,它是在集成电路平面工艺和半导体表面理论高度发展的基础上提出来的。虽然称它为器件,但并不是一般的分立器件,而是一种集成化的功能器件。由于它的结构简单,集成度高,并且具有很独特的功能,所以发展很快。目前已发展成为大规模集成电路的一个重要分支,用途越来起广泛。在数字方面,主要是制作高位数的申行

电荷耦合器件的工作原理,电荷耦合器件结构,电荷耦合器件(CCD),是1970年提出来的一种MOS结构的新型器件,它是在集成电路平面工艺和半导体表面理论高度发展的基础上提出来的。虽然称它为器件,但并不是一般的分立器件,而是一种集成化的功能器件。由于它的结构简单,集成度高,并且具有很独特的功能,所以发展很快。目前已发展成为大规模集成电路的一个重要分支,用途越来起广泛。在数字方面,主要是制作高位数的申行

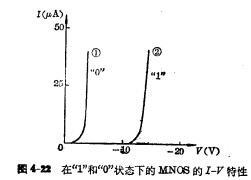

MOS只读存贮器(ROM),MOS只读存贮器工作原理,MOS只读存贮器读写过程,只读存贮器是一种存贮固定不变信息的存贮器,可以存放固定常数、固定的函数和固定的指令等等。使用时只能将这些固定的内容读出来,而不能随时写入新的信息,所以称这种存贮器为只读存贮器。目前,这种存贮器广泛使用在微程序序列发生器、计算机的硬编排子程序、数据表、随机控制逻辑、译码器、字母或字符发生器等方面。由于ROM的线路结构比R

MOS只读存贮器(ROM),MOS只读存贮器工作原理,MOS只读存贮器读写过程,只读存贮器是一种存贮固定不变信息的存贮器,可以存放固定常数、固定的函数和固定的指令等等。使用时只能将这些固定的内容读出来,而不能随时写入新的信息,所以称这种存贮器为只读存贮器。目前,这种存贮器广泛使用在微程序序列发生器、计算机的硬编排子程序、数据表、随机控制逻辑、译码器、字母或字符发生器等方面。由于ROM的线路结构比R

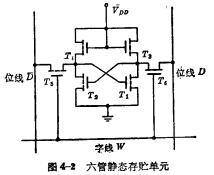

MOS存贮器-随机存取贮器(RAM)结构和读写过程的特征,随机存取存贮器(RAM),由许多存贮单元组成,它的每一个存贮单元,都可按一定要求的顺序,存入或取出所需的二进制信息。MOS随机存取存贮器有静态和动态两种。动态RAM 具有功耗低、集成度高、速度快的优点;静态RAM性能稳定,使用方便。

MOS存贮器-随机存取贮器(RAM)结构和读写过程的特征,随机存取存贮器(RAM),由许多存贮单元组成,它的每一个存贮单元,都可按一定要求的顺序,存入或取出所需的二进制信息。MOS随机存取存贮器有静态和动态两种。动态RAM 具有功耗低、集成度高、速度快的优点;静态RAM性能稳定,使用方便。

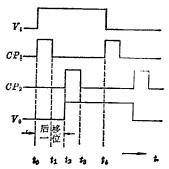

MOS动态移位寄存器的六种特征及工作原理详解分析,上面所述的静态移位寄存器,是利用静态的R-S、J-K或D触发器组成的,性能比较稳定,但电路结构比较复杂,移位速度较慢,集成度也比较低。在大规模集成电路高度发展的今天,功耗低、结构简单、速度快、集成度高的动态移位寄存器充分显示了它的突出优点。动态移位寄存器是由动态逻辑电路构成的。为了理解动态移位寄存器的工作原理,下面我们以NMOS为例,先介绍一下什么

MOS动态移位寄存器的六种特征及工作原理详解分析,上面所述的静态移位寄存器,是利用静态的R-S、J-K或D触发器组成的,性能比较稳定,但电路结构比较复杂,移位速度较慢,集成度也比较低。在大规模集成电路高度发展的今天,功耗低、结构简单、速度快、集成度高的动态移位寄存器充分显示了它的突出优点。动态移位寄存器是由动态逻辑电路构成的。为了理解动态移位寄存器的工作原理,下面我们以NMOS为例,先介绍一下什么

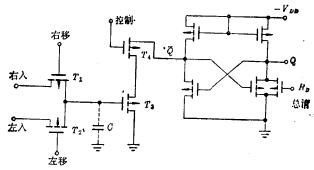

MOS静态移位寄存器,MOS移位寄存器结构,MOS移位寄存器工作原理,移位寄存器是能寄存信息和具有移位功能的逻辑部件。MOS移位寄存器按照结构可分为静态和动态两种。下面将分别介绍这两种移位寄存器的结构及其工作原理。

MOS静态移位寄存器,MOS移位寄存器结构,MOS移位寄存器工作原理,移位寄存器是能寄存信息和具有移位功能的逻辑部件。MOS移位寄存器按照结构可分为静态和动态两种。下面将分别介绍这两种移位寄存器的结构及其工作原理。

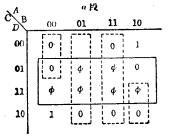

MOS 八段译码器,八段译码器,八段译码器结构,在电子技术高度发展的今天,许多电子仪器所测量得到的数据都可以直接用数码管显示出来,目前常用的有七段、八段数码管。图3-17所示为八段数码管的结构原理。它由八段能发光的线条组成,每条发光元件都有对应的引出线,当引出线处于高电平时,它就发光,低电平时就熄灭。因此可以根据需要显示的数字,在各引出线上施加高电平或低电平,就可显出0~9十个数字。

MOS 八段译码器,八段译码器,八段译码器结构,在电子技术高度发展的今天,许多电子仪器所测量得到的数据都可以直接用数码管显示出来,目前常用的有七段、八段数码管。图3-17所示为八段数码管的结构原理。它由八段能发光的线条组成,每条发光元件都有对应的引出线,当引出线处于高电平时,它就发光,低电平时就熄灭。因此可以根据需要显示的数字,在各引出线上施加高电平或低电平,就可显出0~9十个数字。

MOS 三变量译码器,三变量译码器,三变量译码器结构,图3-15表示一个多路数据传输控制系统,图中的MOS管image.png作为传输门。如果要把数据image.png一个个传输出去,就要用八根控制线分别控制八个门管的栅极。但采用译码器控制,只要三根线就可以了。因为三个二进制变量,可以组成八个状态,即MOS 三变量译码器。

MOS 三变量译码器,三变量译码器,三变量译码器结构,图3-15表示一个多路数据传输控制系统,图中的MOS管image.png作为传输门。如果要把数据image.png一个个传输出去,就要用八根控制线分别控制八个门管的栅极。但采用译码器控制,只要三根线就可以了。因为三个二进制变量,可以组成八个状态,即MOS 三变量译码器。

MOS加法器,MOS半加器,MOS全加器,MOS加法器在电子计算机及其它数字系统中,常采用二进制计数,而在二进制数的运算中,加、减、乘、除最终都可以归纳为加法运算。加法运算是计算机中的重要运算。能完成加法运算的电路称为加法器。

MOS加法器,MOS半加器,MOS全加器,MOS加法器在电子计算机及其它数字系统中,常采用二进制计数,而在二进制数的运算中,加、减、乘、除最终都可以归纳为加法运算。加法运算是计算机中的重要运算。能完成加法运算的电路称为加法器。

MOS D触发器,D触发器特点,D触发器工作原理,D触发器是一个输入端的触发器,其特点是输出与输入具有相同的状态,而与触发器原状态无关。基本的D触发器,是一种信息暂时寄存电路,如图3-9所示。从逻逻辑图上看到,D触发器是在R-S-T触发靠的前面加了一级倒相器,并把这级倒相器的输入端与R-S触发器的S端连接;把它的输出端(即image.png)与R-S触发器的R连接。从逻辑图上看到,当D输入端为“1

MOS D触发器,D触发器特点,D触发器工作原理,D触发器是一个输入端的触发器,其特点是输出与输入具有相同的状态,而与触发器原状态无关。基本的D触发器,是一种信息暂时寄存电路,如图3-9所示。从逻逻辑图上看到,D触发器是在R-S-T触发靠的前面加了一级倒相器,并把这级倒相器的输入端与R-S触发器的S端连接;把它的输出端(即image.png)与R-S触发器的R连接。从逻辑图上看到,当D输入端为“1

MOS J-K管触发器,J-K管触发器工作原理,J-K管设计考虑,J-K触发器也包括主触发器和从触发器,但区别于一般R-S主从触发器。它的特点是:从触发器的两个输出端Q和image.png,分别引回到image.png管的栅极,并由原来R-S触发器的S端改为J输入端,R输入端改为K输入端。因此在J-K触发器里,不仅从触发器要受到主触发器的控制,而主触发器也要受到从触发器的控制。这样改进以后,J-

MOS J-K管触发器,J-K管触发器工作原理,J-K管设计考虑,J-K触发器也包括主触发器和从触发器,但区别于一般R-S主从触发器。它的特点是:从触发器的两个输出端Q和image.png,分别引回到image.png管的栅极,并由原来R-S触发器的S端改为J输入端,R输入端改为K输入端。因此在J-K触发器里,不仅从触发器要受到主触发器的控制,而主触发器也要受到从触发器的控制。这样改进以后,J-